- 您现在的位置:买卖IC网 > Sheet目录3882 > PIC16F87T-E/ML (Microchip Technology)IC MCU FLASH 4KX14 EEPROM 28QFN

54

8008H–AVR–04/11

ATtiny48/88

means that these interrupts can be used for waking the part also from sleep modes other than

Idle mode.

The INT0 and INT1 interrupts can be triggered by a falling or rising edge, or a low level. This is

configured as described in “EICRA – External Interrupt Control Register A” on page 55. When

INT0 or INT1 interrupts are enabled and are configured as level triggered, the interrupts will trig-

ger as long as the corresponding pin is held low. Note that recognition of falling or rising edge

interrupts on INT0 or INT1 requires the presence of an I/O clock, described in “I/O Clock –

9.2.1

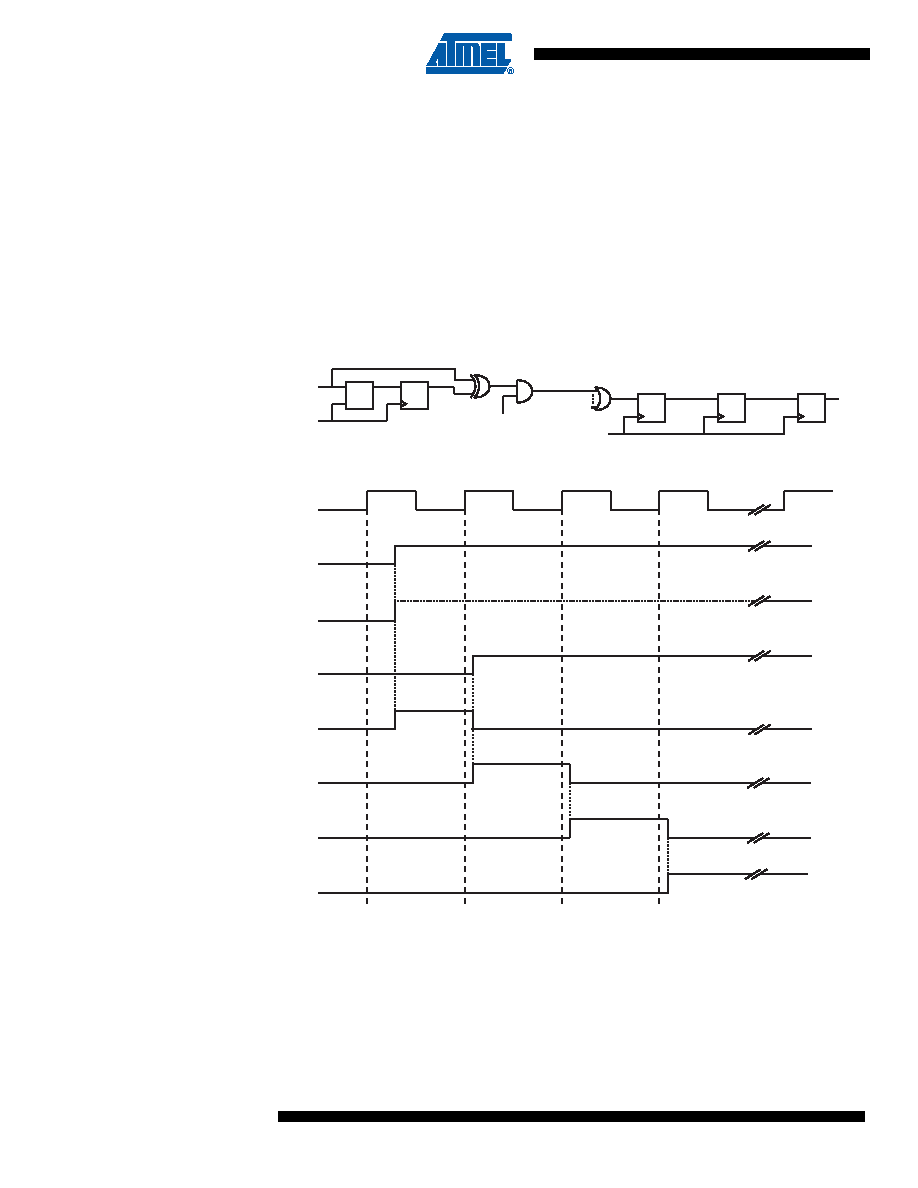

Pin Change Interrupt Timing

An example of timing of a pin change interrupt is shown in Figure 9-1.

Figure 9-1.

Timing of pin change interrupts

9.2.2

Low Level Interrupt

Low level interrupts on INT0 and INT1 are detected asynchronously. This means that the inter-

rupt sources can be used for waking the part also from sleep modes other than Idle (the I/O

clock is halted in all sleep modes except Idle mode).

Note that if a level triggered interrupt is used for wake-up from Power-down, the required level

must be held long enough for the MCU to complete the wake-up to trigger the level interrupt. If

the level disappears before the end of the Start-up Time, the MCU will still wake up, but no inter-

clk

PCINT(0)

pin_lat

pin_sync

pcint_in_(0)

pcint_syn

pcint_setflag

PCIF

PCINT(0)

pin_sync

pcint_syn

pin_lat

D

Q

LE

pcint_setflag

PCIF

clk

PCINT(0) in PCMSK(x)

pcint_in_(0)

0

x

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F87-E/ML

IC MCU FLASH 4KX14 EEPROM 28QFN

PIC18LF4320-I/ML

IC MCU FLASH 4KX16 EEPROM 44QFN

PIC16F77T-I/PTG

IC MCU FLASH 8KX14 W/AD 44TQFP

PIC16LF1933-I/SO

IC PIC MCU FLASH 4K 28-SOIC

PIC16C54C-20I/SO

IC MCU OTP 512X12 18SOIC

PIC16LF726-I/SO

IC PIC MCU FLASH 8K 1.8V 28-SOIC

PIC12CE673-10/P

IC MCU OTP 1KX14 A/D&EE 8DIP

PIC16F726-I/SO

IC PIC MCU FLASH 8KX14 28-SOIC

相关代理商/技术参数

PIC16F87T-E/SO

功能描述:8位微控制器 -MCU 20MHz 4K Flash RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-E/SS

功能描述:8位微控制器 -MCU 20MHz 4K Flash RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-I/ML

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-I/SO

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-I/SS

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F882-E/ML

功能描述:8位微控制器 -MCU 3.5KB Enh FLSH 128 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F882-E/SO

功能描述:8位微控制器 -MCU 3.5KB Enh FLSH 128 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F882-E/SP

功能描述:8位微控制器 -MCU 3.5KB Enh FLSH 128 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT